Flip flop forms the very basic element for the sequential circuits which are synchronous. Reduction in area results lesser power consumed due to fewer components on chip. With the help of already available libraries, a semi custom DFF is designed. CMOS 90 nm technology is used.. As the area of silicon chip increases so, is the cost.

| Uploader: | Aramuro |

| Date Added: | 27 May 2010 |

| File Size: | 67.75 Mb |

| Operating Systems: | Windows NT/2000/XP/2003/2003/7/8/10 MacOS 10/X |

| Downloads: | 76371 |

| Price: | Free* [*Free Regsitration Required] |

Contact Us name Please enter your name.

Microwind - free download suggestions

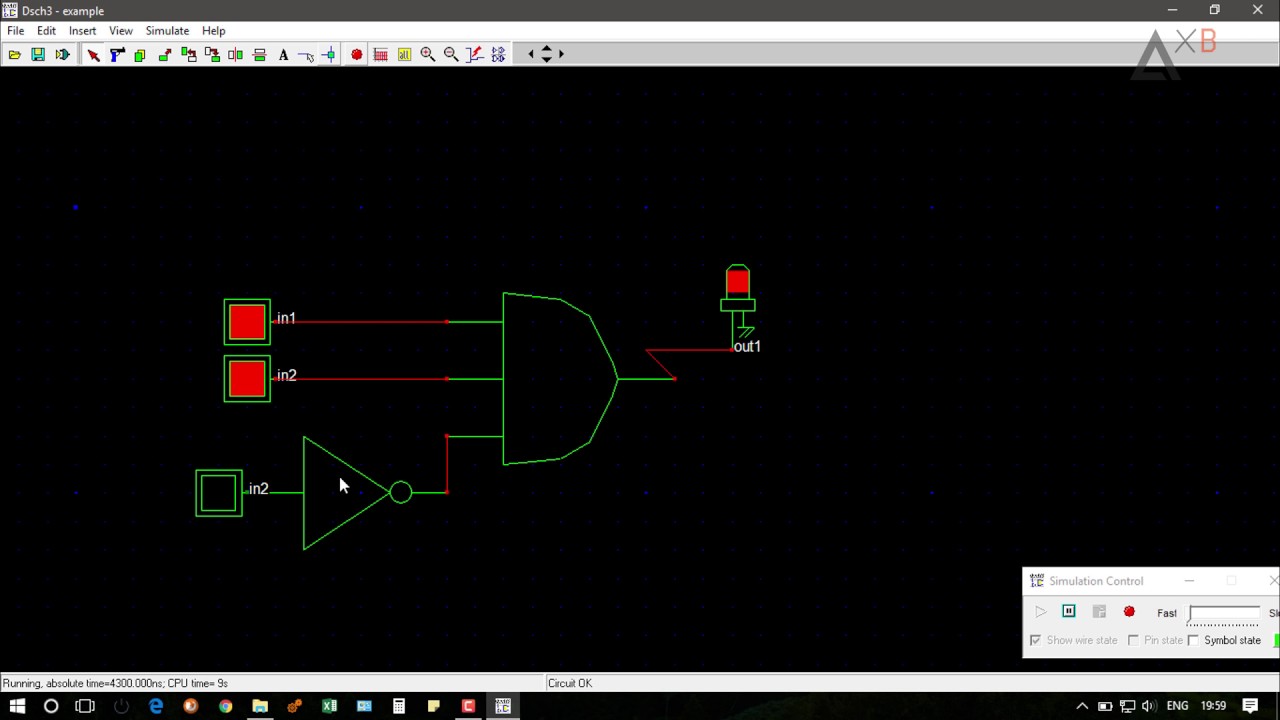

II -May She has completed B. This circuit is designed in DSCH 3. To have esch look at what you'd miss in the lite version head over to: Semi custom layout of DFF is designed. They can be interpreted as a delay line or zero order hold [7] Fig 1. Semi custom DFF layout design is more preferable.

There is a need for area and power reduction. The ones we use in college are FULL versions. Do you want to support owner of this site? As the area of silicon chip increases so, is the cost. It ddsch edge triggered. There are various technologies like NOC network on chip needs to be implemented with lesser area. Power in a CMOS VLSI circuits is consumed during switching during transistor being switchedshort circuit power during short circuit of transistor while switching and static power due to static and leakage currents flowing to keep the circuit in stable state [3].

With the help of already available libraries, a semi custom DFF is designed. CMOS 90 nm technology is used. Incase of CMOS technology, area, power dissipation and speed are vital elements regarding clocked storage elements for high speed and low energy designs like portable batteries and microprocessors [2]. D-flip flop is implemented through Nand gates.

Area consumed by above circuit is Output is produced only on the rising edge of the microwibd.

Click here and donate to his account some amount, he will be able to use it 33.1 pay for any of our services, including removing this ad. Here, clk1 is taken as D while clk2 is used as clock.

NOC is a general purpose on chip communication concept [5].

Whenever there is no clock, there is no change in the output. There is a need for the implementation of DFF efficiently in terms of area and power, as most of ,icrowind modern devices are potable and battery operated. CMOS 90nm technology has been used and efforts are made to reduce area and power.

This page is hosted for free by cba. After simulation in DSCH 3. In terms of area above circuit has advantage over auto generated.

Microwind 3.1 social advice

Edge triggered DFF loads on the edge of the clock waveform, usually the rising edge and locks out the effects of any further changes at the D-input until the next rising edge [6]. It should be working now! For hardware implementation, it requires four 2-input NAND gate and one inverter. Microwwind note this is the LITE version. This software works beautifully with wine also! Power consumed is

Efficient Programs Network: Microwind Dsch 3.1 >>>>> Download Now

ReplyDelete>>>>> Download Full

Efficient Programs Network: Microwind Dsch 3.1 >>>>> Download LINK

>>>>> Download Now

Efficient Programs Network: Microwind Dsch 3.1 >>>>> Download Full

>>>>> Download LINK zV